**PATENT**

# IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

Applicants:

Jae-Yoel KIM et al.

Docket: 678-1367 (P11310)

Serial No.:

10/789,119

Dated: May 26, 2004

Filed:

February 27, 2004

For:

APPARATUS AND METHOD FOR TRANSMITTING/RECEIVING PREAMBLE IN ULTRA WIDEBAND COMMUNICATION SYSTEM

Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

## TRANSMITTAL OF PRIORITY DOCUMENT

Sir:

Enclosed is a certified copy of Korean Appln. No. 2003-12780 filed on February 28, 2003, from which priority is claimed under 35 U.S.C. §119.

Respectfully submitted,

Paul J. Farrell

Registration No. 33,494 Attorney for Applicants

# **DILWORTH & BARRESE, LLP**

333 Earle Ovington Boulevard Uniondale, New York 11553 (516) 228-8484

#### CERTIFICATE OF MAILING UNDER 37 C.F.R. § 1.8 (a)

I hereby certify that this correspondence is being deposited with the United States Postal Service as first class mail, postpaid in an envelope, addressed to the: Commissioner of Patents, P.O. Box 1450, Alexandria, VA 22313-1450 on May 26, 2004.

Dated: May 26, 2004

Paul I. Farrell

This is to certify that the following application annexed hereto is a true copy from the records of the Korean Intellectual Property Office.

출 원 번 호

10-2003-0012780

Application Number

출 원 년 월 일

Date of Application

2003년 02월 28일

FEB 28, 2003

`

인 :

삼성전자주식회사

SAMSUNG ELECTRONICS CO., LTD.

2004 년 02 월 23 일

특 허 청

COMMISSIONER

【서지사항】

【서류명】 특허출원서

【권리구분】 특허

【수신처】 특허청장

【참조번호】 0003

【제출일자】 2003.02.28

【국제특허분류】 H04Q

【발명의 명칭】 초광대역 통신 시스템의 프리앰블 송수신 장치 및 방법

【발명의 영문명칭】 APPARATUS FOR TRANSMITTING/RECEIVING PREAMBLE IN ULTRA WIDE

BAND COMMUNICATION SYSTEM AND METHOD THEREOF

【출원인】

【명칭】 삼성전자 주식회사

【출원인코드】 1-1998-104271-3

【대리인】

【성명】 이건주

[대리인코드] 9-1998-000339-8

【포괄위임등록번호】 2003-001449-1

【발명자】

【성명의 국문표기】 김재열

【성명의 영문표기】 KIM, Jae Yoel

【주민등록번호】 700219-1047637

【우편번호】 435-042

【주소】 경기도 군포시 산본2동 산본9단지 백두아파트 960동 1401호

【국적】 KR

【발명자】

【성명의 국문표기】 김형관

【성명의 영문표기】KIM, Hyoung Gwan【주민등록번호】740217-1001013

【우편번호】 110-320

【주소】 서울특별시 종로구 낙원동 284-6 15통2반 낙원아파트 913호

【국적】 KR

【발명자】

【성명의 국문표기】 박성일

【성명의 영문표기】 PARK,Seong III

. 0030012780 출력 일자: 2004/2/24

【주민등록번호】 680519-1481421

【우편번호】 463-776

【주소】 경기도 성남시 분당구 서현동(시범단지) 한양아파트 325동 801

호

【국적】 KR

【발명자】

【성명의 국문표기】 김선용

【성명의 영문표기】 KIM,Sun Yong

【주민등록번호】 680130-1143417

【우편번호】 158-070

【주소】 서울특별시 양천구 신정동 목동아파트 913동 405

【국적】 KR

【취지】 특허법 제42조의 규정에 의하여 위와 같이 출원합니다. 대리인

이건주 (인)

【수수료】

【기본출원료】 20 면 29,000 원

【가산출원료】 33 면 33,000 원

【우선권주장료】

0

건

0

원

【심사청구료】

0

항

0

원

【합계】 62,000 원

# 【요약서】

## [요약]

본 발명은 초광대역 통신 시스템에 관한 것으로서, 물리 계층 프레임의 프리앰블을 비주기적 상관 특성을 가지는 비주기적 시퀀스를 사용하여 동기 획득용 프리앰블인 제1프리앰블과, 상기비주기적 시퀀스 혹은 주기적 상관 특성을 가지는 주기적 시퀀스를 사용하여 채널 추정용 프리앰블인 제2프리앰블로 각각 생성한 후, 상기 제1프리앰블과 상기 제2프리앰블을 다중화하여 상기 초광대역 통신 시스템의 프리앰블로 송신한다.

#### 【대표도】

도 13

# 【색인어】

제1프리앰블, 제2프리앰블, 동기 획득, 채널 추정, ARM 시퀀스, CAZAC 시퀀스

#### 【명세서】

#### 【발명의 명칭】

초광대역 통신 시스템의 프리앰블 송수신 장치 및 방법{APPARATUS FOR

TRANSMITTING/RECEIVING PREAMBLE IN ULTRA WIDE BAND COMMUNICATION SYSTEM AND METHOD

THEREOF}

#### 【도면의 간단한 설명】

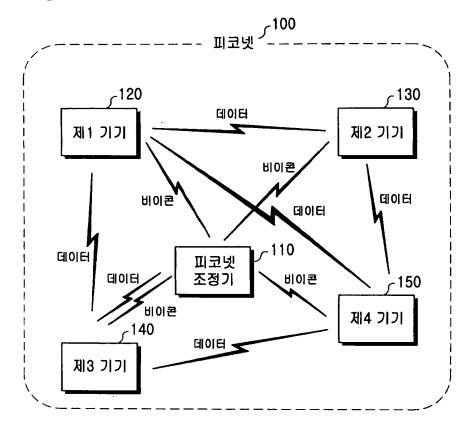

도 1은 일반적인 초광대역 통신 시스템의 피코넷을 개략적으로 도시한 도면

도 2는 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우 및 55Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임 구조를 개략적으로 도시한 도면

도 3은 전송 속도가 11Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임 구조를 개략적으로 도시한 도면

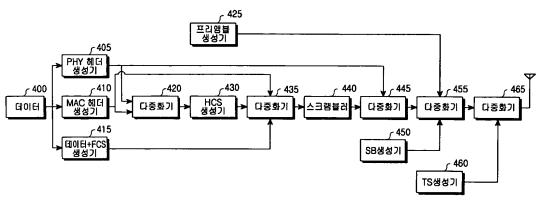

도 4는 도 2의 물리 계층 프레임을 송신하는 물리 계층 프레임 송신 장치 내부 구조를 개략적으로 도시한 도면

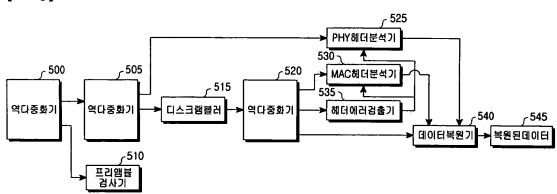

도 5는 도 4의 물리 계층 프레임 송신 장치에 상응하는 물리 계층 프레임 수신 장치 내부 구조를 개략적으로 도시한 도면

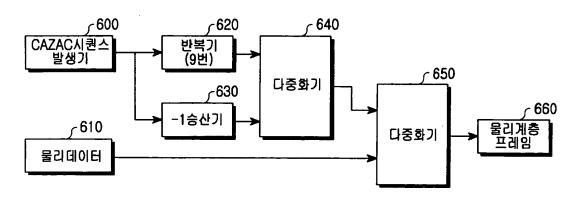

도 6은 도 4의 물리 계층 프레임 송신 장치에서 프리앰블 생성기 구조를 상세하게 도시 한 도면

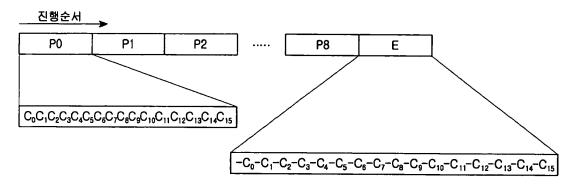

도 7은 일반적인 초광대역 통신 시스템의 물리 계층 프레임내 프리앰블 구조를 개략적으로 도시한 도면

도 8은 일반적인 길이 16인 CAZAC 시퀀스의 엘리먼트 값들을 도시한 테이블

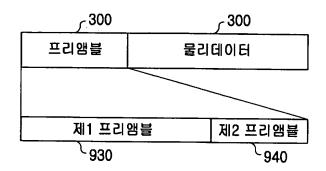

도 9는 본 발명의 실시예에 따른 초광대역 통신 시스템의 물리 계층 프레임 구조를 개략 적으로 도시한 도면

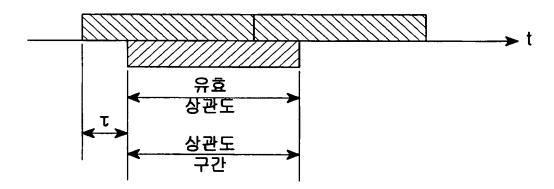

도 10은 주기적 시퀀스 자기 상관도 검출을 개략적으로 도시한 도면

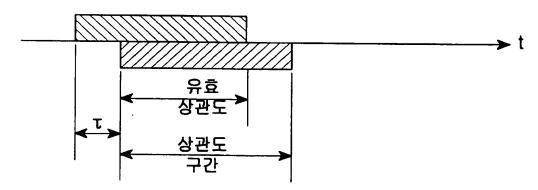

도 11은 비주기적 시퀀스의 자기 상관도 검출을 개략적으로 도시한 도면

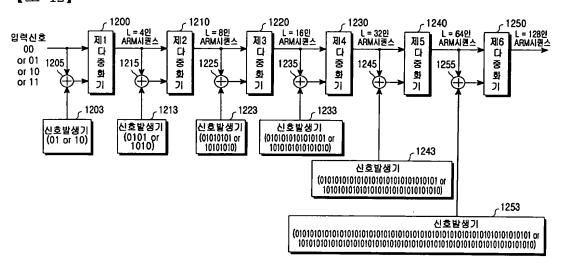

도 12는 도 9의 제1프리앰블(930)에 적용할 ARM 시퀀스 생성 장치 내부 구조를 도시한 도면

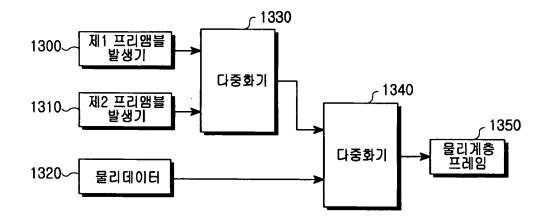

도 13은 도 9의 물리 계층 프레임을 송신하는 물리 계층 프레임 송신 장치 내부 구조를 개략적으로 도시한 도면

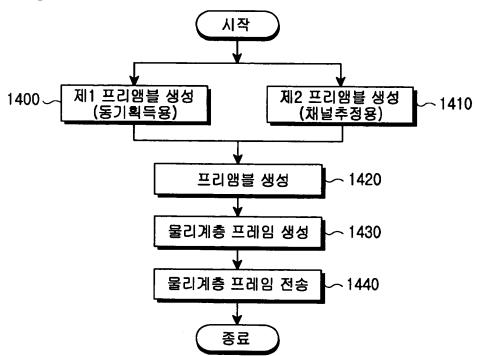

도 14는 도 13에 상응하는 물리 계층 프레임 송신 과정을 도시한 순서도

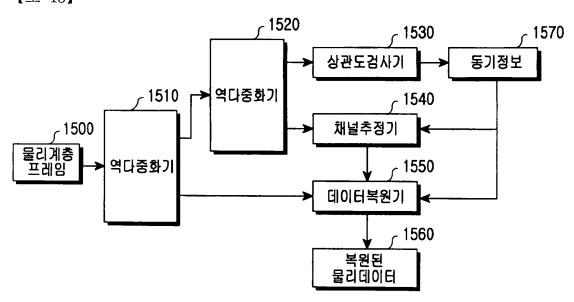

도 15는 도 13에 상응하는 물리 계층 프레임 수신 장치 내부 구조를 개략적으로 도시한 도면

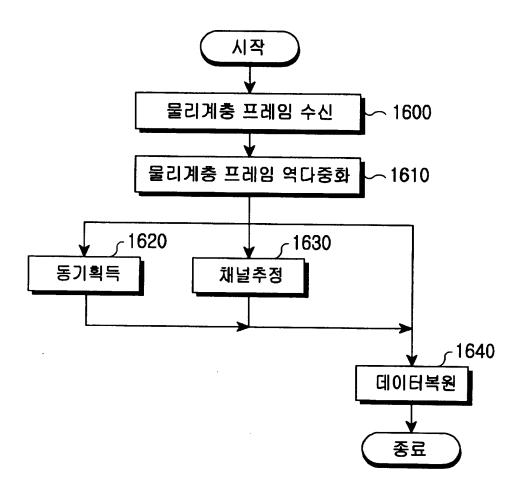

도 16은 도 15에 상응하는 물리 계층 프레임 수신 과정을 도시한 순서도

【발명의 상세한 설명】

【발명의 목적】

【발명이 속하는 기술분야 및 그 분야의 종래기술】

본 발명은 초광대역 통신 시스템에 관한 것으로서, 특히 동기 획득용과 채널 추정용 프리앰블을 분리하여 프리앰블을 생성하는 장치 및 방법에 관한 것이다.

의반적으로, 초광대역(UWB: Ultra Wide Band) 통신 시스템은 근거리 무선 통신 시스템으로서, IEEE(Institute of Electrical and Electronics Engineers) 802.15.3a 표준 규격에서 논의되고 있는 무선 통신 시스템이다. 상기 초광대역 통신 시스템은 근거리, 일 예로 10m이내의 근거리 고속 무선 통신을 위한 기술로서, 도 1을 참조하여 상기 초광대역 통신 시스템을 설명하기로 한다.

<19> 상기 도 1은 일반적인 초광대역 통신 시스템의 피코넷을 개략적으로 도시한 도면이다.

상기 도 1을 설명하기에 앞서, 상기 초광대역 통신 시스템은 그 무선 통신 특성상 근거리 무선 통신을 타겟(target)으로 하고 있으며, 따라서 홈 네트워크(home network) 혹은 근거리 레이터(radar) 등에 적용될 것으로 예상된다. 그리고, 상기 초광대역 통신 시스템은 그 무선 통신의 기본 단위로서 피코넷(Piconet)을 사용한다.

\*21> 상기 도 1을 참조하면, 먼저 피코넷(100)은 피코넷 조정기(PNC: Pico Net Coordinator)(100)와, 다수의 기기들, 즉 제1기기(120)와, 제2기기(130)와, 제3기기(140)와, 제4기기(150)로 구성된다. 상기 피코넷 조정기(110)는 상기 제1기기(120)와, 제2기기(130)와, 제3기기(140)와, 제4기기(150)로 비이콘(beacon)을 송신하여 상기 제1기기(120)와, 제2기기(130)와, 제3기기(140)와, 제4기기(150)의 동작을 제어한다. 여기서, 상기 비이콘은 상기 피코넷 조정기(110)에서 발생하는 일종의 제어 신호로서, 상기 비이콘을 수신한 제1기기(120)와, 제2기기(130)와, 제3기기(140)와, 제4기기(150)는 상기 비이콘에 상응하게 그 동작을 조정하게된다. 또한, 상기 피코넷 조정기(110)는 상기 제1기기(120)와, 제2기기(130)와, 제3기기(140)와, 제4기기(150)는 상기 제1기기(120)와, 제2기기(130)와, 제3기기(140)와, 제4기기(150)로 데이터(data)를 전송할 수 있으며, 또한 상기 제1기기(120)와, 제2기기 (130)와, 제3기기(140)와, 제4기기(150)와, 제3기기(140)와, 제4기기(150)와, 제3기기(140)와, 제3기기(140)와, 제4기기(150)와, 제4기기(150)와, 제3기기(140)와, 제4기기(150)와, 제4기기(150)와, 제4기기(150)와, 제4기기(150)와, 제2기기(150)와, 제3기기(140)와, 제4기기(150)와, 제4기기(150)와, 제4기기(150)와, 제2기기(150)와, 제2기기(150)와, 제2기기(150)와, 제3기기(140)와, 제4기기(150)와, 제4기기(150)와, 제4기기(150)와, 제2기기(150)와, 제2기기(150)와

제1기기(120)와, 제2기기(130)와, 제3기기(140)와, 제4기기(150)는 무선 통신을 수행하는 것이 가능한 모든 기기들을 나타내며, 일 예로, 텔레비전과, 모뎀(MODEM)과, VTR, 자동차 등과 같은 기기들을 나타낸다. 이렇게 무선 통신이 가능한 기기들간에는 상기 도 1에 도시한 바와 같은 피코넷(100)을 형성할 수 있으며, 상기 피코넷(100)의 전반적인 동작 제어를 상기 피코넷 조정기(110)가 수행하는 것이다.

(222) 또한, 상기 초광대역 통신 시스템은 근거리 구간에서 비교적 낮은 전력으로 비교적 넓은 주파수 대역을 사용하여 비교적 많은 양의 데이터를 고속으로 전송하는 시스템이다. 상기 초광대역 통신 시스템의 용량(capacity)은 대역폭(bandwidth)과 신호대 잡음비(SNR: Signal to Noise Ratio)와 비례한다. 상기 초광대역 통신 시스템은 신호의 확산 특성, 즉 시간 도메인 (domain) 상에서 주기가 매우 짧은 필스(pulse)를 송신하게 되면, 상기 펄스 신호는 주파수 도메인상에서 아주 넓게 확산된다는 원리를 이용한 시스템이다. 결과적으로, 매우 짧은 주기를 갖는 펄스열들을 확산시켜 통신을 수행함으로써, 펄스의 주기를 매우 짧게 하는 것을 가능하게하고, 잡음의 전파 기준으로 삼고 있는 주파수당 송신 에너지 밀도보다 낮출 수 있도록 하는 시스템이 상기 초광대역 통신 시스템이다. 상기 초광대역 통신 시스템에서는 펄스의 파형에 따라서 전송 주파수 대역이 결정된다. 주파수 특성상 초광대역 주파수는 확산 대역을 넓게 하므로 장애물이 많은 장소에서도 페이딩(fading) 현상에 강하며, 잡음보다 주파수당 송신 에너지 밀도가 낮으므로 전력소모가 작다.

한편, 일반적으로 무선 통신 시스템은 송신기와 수신기간에 동기가 정확하게 일치해야만 동작하는 것이 가능하다. 상기 초광대역 통신 시스템 역시 무선 통신 시스템이기 때문에 송신 기와 수신기간의 동기가 정확하게 일치해야만 한다. 일반적으로, 상기 송신기와 수신기간의 동 기를 일치시키기 위해서는 물리 계층(physical layer) 프레임에서 프리앰블(preamble) 시퀀스

를 사용한다. 상기 초광대역 통신 시스템의 물리 계층 프레임 구조는 2가지, 즉 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우와 및 55Mb/s일 경우에 적용되는 제1프레임 구조와, 전송 속도가 11Mb/s 일 경우에 적용되는 제2프레임 구조의 2가지 구조를 가진다. 그러면 여기서 상기 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우 및 55Mb/s일 경우에 적용되는 제1프레임 구조를 도 2를 참조하여 설명하기로 한다.

상기 도 2는 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우 및 55Mb/s

일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임 구조를 개략적으로 도시한 도면이다.

상기 도 2를 참조하면, 먼저 상기 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우 및 55Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임은 프리앰블(200)과, 물리(PHY: physical, 이하 "PHY"라 청하기로 한다) 헤더(header)(210)와, 매체 접속 제어(MAC: Media Access Control, 이하 "MAC"이라 칭하기로 한다) 헤더(220)와, 헤더 검사 시퀀스(HCS: Header Check Sequence, 이하 "HCS"라 청하기로 한다)(230)와, 데이터 + 프레임 검사 시퀀스(FSC: Frame Check Sequence, 이하 "FCS"라 칭하기로 한다)(240)와, 스터브 비트들(SB: Stuff Bits, 이하 "SB"라 칭하기로 한다)(250)과, 테일 심벌들(TS: Tail Symbols, 이하 "TS"라 칭하기로 한다)(260)로 구성된다. 상기 프리앰블(200)은 길이 160의 QPSK(Quadrqture Phase Shift Keying) 심벌이며, 송수신기간 동기 획득 및 반송파(carrier)의 오프셋(offset) 복구 및 수신 신호의 등화(equalization)를 위해 사용된다. 상기 PHY 헤더(210)는 2 옥텟(octet) 길이를 가지며, 스크램블링 코드(scrambling code)와 MAC 프레임의 전송 속도와, 데이터 길이 등에 관한 정보를 나타내기 위해 사용된다. 여기서, 1옥텟은 8비트 길이를 의미한다. 상기 MAC 헤더(220)는 10 옥텟 길이를 가지며, 프레임 조정 신호와, 피코넷 식

별자(PNID: PicoNet IDentifier, 이하 "PNID"라 칭하기로 한다)와, 데스티네이션 식별자 (DestID: Destination IDentifier, 이하 "DestID"라 칭하기로 한다)와, 소스 식별자(SrcID: Source IDentifier, 이하 "SrcID"라 칭하기로 한다)와, 분할 제어(Fragmentation control, 이 하 "Fragmentation control"라 칭하기로 한다) 정보와, 스트림 인덱스(Stream index) 정보를 나타내기 위해 사용된다. 상기 HCS(230)는 2 옥텟 길이를 가지며, 상기 PHY 헤더(210)와 MAC 헤더(220)의 오류 검출(error detection)을 위해 사용된다. 상기 데이터 + FCS(240)에서, 데이 터는 0~2048 옥텟 길이를 가지며, 전송하려는 정보와 암호 정보 전송을 위해 사용된다. 여기서, 상기 데이터는 그 길이가 0~2048 옥텟 중 어느 길이를 가져도 상관없으며, 따라서 유 동적인 크기의 정보 및 암호 정보 전송을 가능하게 한다. 또한, 상기 데이터 + FCS(240)에서, FCS는 4 옥텟 길이를 가지며, 상기 전송되는 데이터의 오류를 검출하기 위해 사용된다. 상기 SB(250)는 상기 데이터 + FCS(240)의 크기가 전송하려는 전송 속도에 적용되는 심볼 크기의 정 수배가 아닐 때, 상기 데이터 + FCS(240)의 크기를 상기 전송 속도에 적용되는 심볼 크기의 정 수배로 생성하기 위해 삽입되는 일종의 더미 비트들(dummy bits)이다. 물론, 상기 데이터 + FCS(240)의 크기가 전송하려는 전송 속도에 적용되는 심볼 크기의 정수배가 되면 상기 SB(250) 는 삽입될 필요가 없으며, 실제 상기 초광대역 통신 시스템에서 전송 속도가 11Mb/s일 경우 물 리 계층 프레임에 상기 SB(250)는 삽입되지 않는다. 이는 하기 도 3에서 상세히 설명할 것이므 로 여기서는 그 상세한 설명을 생략하기로 한다. 상기 TS(260)는 트렐리스(trellis)의 초기 상 태를 나타내기 위해서 사용된다.

<26> 상기 도 2에서는 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우 및 55Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임 구조를 설명하였으며, 다

음으로 도 3을 참조하여 전송 속도가 11Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리계층 프레임 구조를 설명하기로 한다.

<27> 상기 도 3은 전송 속도가 11Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임 구조를 개략적으로 도시한 도면이다.

상기 도 3을 참조하면, 먼저 전송 속도가 11Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임은 프리앰블(300)과, PHY 헤더 + MAC 헤더 + HCS(310)와, PHY 헤더 + MAC 헤더 + HCS(320)와, 데이터 + FCS(330) 및 TS(340)로 구성된다. 상기 도 2에서 설명한, 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우 및 55Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임 구조와 상기 도 3에 도시한 전송 속도가 11Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임 구조는 유사한 구조를 가지지만, 상기 전송 속도가 11Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임은 헤더부분의 오류 발생 비율을 최소화시키기 위해서 PHY 헤더와, MAC 헤더와, HCS가 한번 더 반복되는 것이다. 이렇게 반복 삽입된 PHY 헤더 + MAC 헤더 + HCS(320)는 상기 데이터 + FCS(330) 및 TS(340)와 함께 동일한 블록(block)처럼 취급되어 변복조된다. 그리고, 상기 도 2에서 설명한바와 같이 전송 속도가 11Mb/s일 경우 상기 데이터 + FCS(330)의 크기가 전송하려는 속도, 즉 11Mb/s에 적용되는 심볼 크기의 정수배가 되기 때문에 별도로 SB를 삽입할 필요가 없으며, 따라서 상기 전송 속도가 11Mb/s일 경우 물리 계층 프레임에 상기 SB는 삽입되지 않는다.

다음으로 도 4를 참조하여 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우 및 55Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임 송신 장치를 설명하기로 한다. 여기서, 설명의 편의상 상기 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와.

44Mb/s일 경우 및 55Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임 송신 장치만을 설명하기로 함에 유의하여야 한다.

<30> 상기 도 4는 도 2의 물리 계층 프레임을 송신하는 물리 계층 프레임 송신 장치 내부 구조를 개략적으로 도시한 도면이다.

\*31> 상기 도 4를 참조하면, 먼저 전송할 데이터(400)가 전달되면, 상기 데이터(400)는 PHY 해더 생성기(405)와, MAC 해더 생성기(410)와, 데이터 + FCS 생성기(415)로 입력된다. 상기 PHY 해더 생성기(405)는 상기 입력되는 데이터(400)에 상용하게 PHY 해더, 즉 스크램블링 코드와, MAC 프레임의 전송 속도 및 데이터 길이 등에 대한 정보를 포함하는 PHY 해더를 생성한 후 다중화기(MUX)(420) 및 다중화기(445)로 출력한다. 상기 MAC 해더 생성기(410)는 상기 입력되는 데이터(400)에 상용하게 MAC 해더, 즉 프레임 조정 신호와, PNID와, DestID와, SrcID와, Fragmentation control 정보 및 스트림 인덱스 정보를 포함하는 MAC 해더를 생성한 후 상기 다중화기(420) 및 다중화기(435)로 출력한다. 상기 데이터 + FCS 생성기(415)는 상기 입력되는데이터(400)에 상용하게 데이터 + FCS를 생성한 후 상기 다중화기(435)로 출력한다. 여기서,데이터 + FCS 생성기(415)는 생성된 데이터와, 상기 데이터에 상용하게 32비트 순환 리턴던시 검사(CRC: Cyclic Redundancy Check, 이하 "CRC"라 칭하기로 한다)인 FCS를 삽입하여 출력하는 것이다.

《32》 상기 다중화기(420)는 상기 PHY 헤더 생성기(405)와 상기 MAC 헤더 생성기(410)에서 출력한 신호들을 상기 도 2에서 설명한 물리 계층 프레임 구조에 상응하게 다중화한 후 HCS 생성기(430)로 출력한다. 상기 HCS 생성기(430)는 상기 다중화기(420)에서 출력한 신호, 즉 PHY 헤더와, MAC 헤더에 상응하게 HCS를 생성한 후 상기 다중화기(435)로 출력한다. 상기 다중화기(435)는 상기 MAC 헤더 생성기(410)와 데이터 + FCS 생성기(415)에서 출력한 신호를 상기 도 2

에서 설명한 물리 계층 프레임 구조에 상응하게 다중화한 후 스크램블러(scrambler)(440)로 출력한다. 상기 스크램블러(440)는 상기 다중화기(435)에서 출력한 신호를 입력하여 미리 설정되어 있는 스크램블링 코드를 가지고 스크램블링한 후 상기 다중화기(445)로 출력한다. 상기 다중화기(445)는 상기 PHY 헤더 생성기(405)에서 출력한 신호와, 상기 스크램블러(440)에서 출력한 신호를 상기 도 2에서 설명한 물리 계층 프레임 구조에 상응하게 다중화한 후 다중화기(455)로 출력한다.

상기 도 4에서는 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우 및 55Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임 생성 장치를 설명하였으며, 다음으로 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우 및 55Mb/s일 경우에 적용되는 초광대역 통신 시스템의 물리 계층 프레임 수신 장치를 도 5를 참조하여 설명하기로 한다.

<35> 상기 도 5는 도 4의 물리 계층 프레임 송신 장치에 상응하는 물리 계층 프레임 수신 장치 내부 구조를 개략적으로 도시한 도면이다.

상기 도 5를 참조하면, 먼저 안태나를 통해 신호가 수신되면, 상기 수신된 신호는 역다 중화기(DEMUX)(500)로 입력된다. 상기 역다중화기(500)는 상기 수신 신호를 상기 도 2에서 설명한 물리 계층 프레임 구조에 상응하게 역다중화하여 역다중화기(505) 및 프리앰블 검사기(510)로 출력한다. 여기서, 상기 역다중화기(500)는 상기 수신 신호를 상기 도 2에서 설명한 물리 계층 프레임 구조에 상응하게 역다중화하여, 즉 프리앰블과 나머지 필드들, 즉 PHY 헤더와, MAC 헤더와, HCS와, 데이터 + FCS와, SB 및 TS로 역다중화하여 상기 프리앰블은 프리앰블 검사기(510)로 출력하고, 나머지 필드들은 역다중화기(505)로 출력한다. 여기서, 설명의 편의 상 상기 물리 계층 프레임에서 상기 프리앰블을 제외한 나머지 필드들중에서 상기 SB 및 TS에 대해서는 본 발명과 직접적인 연판이 없으므로 여기서는 그 상세한 설명을 생략하기로 한다. 상기 프리앰블 검사기(510)은 상기 역다중화기(500)에서 출력한 프리앰블을 입력하고, 상기 입력한 프리앰블을 가지고 송신기와 동기를 획득하고, 또한 채널 추정(channel estimation)을 수 행한다.

○37> 한편, 상기 역다중화기(505)는 상기 역다중화기(500)에서 출력한 신호를 입력하여 상기도 2에서 설명한 물리 계층 프레임 구조에 상응하게 역다중화하여 디스크램블러 (de-scrambler)(515) 및 PHY 헤더 분석기(525)로 출력한다. 여기서, 상기 역다중화기(505)는 상기 프리앰블이 제거된 나머지 필드들중 PHY 헤더를 상기 PHY 헤더 분석기(525)로 출력하고, 나머지 필드들은 다시 디스크램블러(515)로 출력하는 것이다. 상기 PHY 헤더 분석기(525)는 상기 역다중화기(505)에서 출력한 PHY 헤더를 분석하여 스크램블링 코드와 MAC 프레임의 전송 속도와, 데이터 길이 등에 관한 정보를 추출한 후 데이터 복원기(540)로 출력한다. 상기 디스크

램블러(515)는 상기 역다중화기(505)에서 출력한 신호를 입력하여 물리 계층 송신기에서 적용한 스크램블링 코드와 동일한 스크램블링 코드를 가지고 디스크램블링한 후 역다중화기(520)로 출력한다. 상기 역다중화기(520)는 상기 디스크램블러(515)에서 출력한 신호를 입력하여 상기도 2에서 설명한 물리 계층 프레임 구조에 상응하게 역다중화하여 MAC헤더는 MAC 헤더 분석기(530)로, HCS는 헤더 에러 검출기(535)로, 데이터 + FCS는 상기 데이터 복원기(540)로 출력한다.

상기 MAC 헤더 분석기(530)은 상기 역다중화기(520)에서 출력한 MAC 헤더를 입력하여, 프레임 조정 신호와, PNID와, Dest ID와, SrcID와, Fragmentation control 정보 및 스트림 인덱스 정보를 추출하여 상기 데이터 복원기(540)로 출력한다. 상기 헤더 에러 검출기(535)는 상기역다중화기(520)에서 출력한 HCS를 입력하여, 상기 PHY 헤더와 MAC 헤더의 에러를 여부를 검출한 후 그 결과를 상기 PHY 헤더 분석기(525) 및 MAC 헤더 분석기(530)로 출력한다. 또한, 상기 헤더 에러 검출기(535)는 상기 PHY 헤더와 MAC 헤더에 에러가 발생하였다고 판단하면 더 이상 상기 물리 계층 프레임 처리 과정을 수행하지 않는다. 또한, 상기 데이터 복원기(540)는 상기 PHY 헤더 분석기(525)에서 출력한 정보와, MAC 헤더 분석기(530)에서 출력한 정보를 이용하여 상기 역다중화기(520)에서 출력한 데이터를 복원한다. 여기서, 상기 역다중화기(520)는 데이터 + FCS를 출력하였으며, 상기 데이터 복원기(540)는 상기 FCS를 가지고 에러 발생 여부를 판단하며, 상기 판단 결과 상기 데이터가 에러가 없다고 판단되면 상기 데이터에 대한 복원 동작을 수행하는 것이다. 이렇게, 상기 데이터 복원기(540)에서 복원된 데이터(545)가 송신기에서 건송한 데이터가 되는 것이다.

<39> 다음으로, 도 6을 참조하여 도 4에서 설명한 물리 계층 프레임 송신 장치에서 프리앰블 생성기(425) 구조를 설명하기로 한다.

<40> 상기 도 6은 도 4의 물리 계층 프레임 송신 장치에서 프리앰블 생성기 구조를 상세하게 도시한 도면이다.

생기도 6을 설명하기에 앞서, 상기도 6에 도시한 물리 계층 프레임 송신 장치는 상기도 4에서 설명한 물리 계층 프레임 송신 장치와 동일한 장치이며, 다만 상기도 4에서 설명한 프리앰블 생성기(425) 구조를 상세하게 개시하고 있다는 점에서 상이할 뿐이다. 또한, 상기 프리앰블만을 구체적으로 설명하기 위해서 상기 물리 계층 프레임에서 상기 프리앰블을 제외한 나머지 신호들, 즉 PHY 헤더와, MAC 헤더와, HCS와, 데이터 + FCS와, SB 및 TS를 "물리 데이터 "라고 정의하기로 한다. 상기도 6을 참조하면, 먼저 CAZAC(Constant Amplitude Zero Auto Correlation) 시퀀스 발생기(600)는 길이 16의 CAZAC 시퀀스를 발생한 후 반복기 (repeater)(620) 및 -1 승산기(630)로 출력한다. 여기서, 상기 초광대역 통신 시스템이 그 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우 및 55Mb/s일 경우에 적용되는 물리 계층 프레임에서 프리앰블은 길이 160의 심벌들을 가지기 때문에 상기 CAZAC 시퀀스 발생기(600)에서 발생된 길이 16의 CAZAC 시퀀스는 반복되어야만 하고, 따라서 상기 CAZAC 시퀀스 발생기(600)에서 발생된 길이 16의 CAZAC 시퀀스는 상기 반복기(620)로 출력되는 것이다. 또한, 상기 프리앰블을 제외한 기타신호(610)는 다중화기(650)로 입력된다.

생기 반복기(620)는 상기 CAZAC 시퀀스 발생기(600)에서 출력한 길이 16의 CAZAC 시퀀스를 9번 반복한 후 다중화기(640)로 출력한다. 또한, 상기 -1 승산기(630)는 상기 CAZAC 시퀀스발생기(600)에서 출력한 길이 16의 CAZAC 시퀀스에 -1을 곱한 후 상기 다중화기(640)로 출력한다. 상기 다중화기(640)는 상기 반복기(620)에서 출력한 길이 144의 CAZAC 시퀀스와, 상기 -1 승산기(630)에서 출력한 -1이 곱해진 길이 16의 CAZAC 시퀀스를 다중화하여 다중화기(650)로 출력한다. 여기서, 상기 다중화기(640)는 상기 반복기(620)에서 출력한 길이 144의 CAZAC

시퀀스에 연속하여 상기 1 승산기(630)에서 출력한 -1이 곱해진 길이 16의 CAZAC 시퀀스를 가산하여 프리앰블 신호를 생성한다. 상기 -1 승산기(630)가 상기 CAZAC 시퀀스 발생기(600)에서 출력한 길이 16의 CAZAC 시퀀스에 -1을 곱하는 이유는 상기 -1이 심벌이 곱해진 CAZAC 시퀀스로 프리앰블이 종료됨을 나타내기 위해서이다. 상기 다중화기(650)는 상기 다중화기(640)에서 출력한 신호와 상기 기타신호(610)를 상기 도 2에서 설명한 물리 계층 프레임 구조에 상응하게 다중화여 물리 계층 프레임(660)으로 출력한다.

<43> 그러면 여기서 상기 도 6의 다중화기(640)에서 출력하는 프리앰블 구조를 도 7을 참조하여 설명하기로 한다.

<44> 상기 도 7은 일반적인 초광대역 통신 시스템의 물리 계층 프레임내 프리앰블 구조를 개략적으로 도시한 도면이다.

상기 도 7을 참조하면, 상기 도 6에서 설명한 바와 같이 초광대역 통신 시스템은 프리앰블로서 CAZAC 시퀀스를 사용한다. 그리고, 상기 도 6의 AZAC 신호 발생기(600)에서 출력한 길이 16의 CAZAC 시퀀스를 PO라고 할 때, 상기 PO는 반복기(620)에서 9번 반복된다. 상기 도 7에서 상기 PO가 9번 반복되어 PO 내지 P8로 생성된 것이다. 그리고, 상기 도 6의 -1 승산기(630)에서 상기 PO에 -1을 승산한 CAZAC 시퀀스를 E라고 한다. 상기 도 6에서 설명한 바와 같이 상기 E는 프리앰블이 종료됨을 나타낸다. 즉, 상기 PO 내지 P8과, E가 순차적으로 연집되어 하나의 프리앰블을 생성하고, 상기 PO 내지 P8과, E가 순차적으로 연집되어 하나의 프리앰블을 생성하고, 상기 PO 내지 P8과, E가 순차적으로 연집된 프리앰블을 가지고 동기획득 및 채널 추정을 수행하게 되는 것이다.

<46> 다음으로 도 8을 참조하여 CAZAC 시퀀스의 엘리먼트들 값을 설명하기로 한다.

<47> 상기 도 8은 일반적인 길이 16인 CAZAC 시퀀스의 엘리먼트 값들을 도시한 테이블이다.

상기 도 8을 참조하면, 먼저 CAZAC 시퀀스는 모든 엘리먼트(element)들의 크기가 항상일정한 상수값을 가지며, 영 자기 상관(zero autocorrelation) 특성을 가진 시퀀스를 나타낸다. 여기서, 상기 영 자기상관 특성이란 동기가 일치했을 경우에는 자기 상관도가 시퀀스값과 상기 엘리먼트들의 크기값의 곱의 값을 가지게 되고, 동기가 일치하지 않았을 경우에는 자기 상관도가 0을 가지는 특성을 나타낸다. 상기 CAZAC 시퀀스는 상관도 특성이 우수하고, 채널 추정에 대해 좋은 특성을 가진다는 장점을 가지고 있으나, 변조 방식에 따라서 시퀀스 크기가 제한되는 단점을 지니고 있다. 일 예로, BPSK(Binary Phase Shift Keying) 변조 방식을 사용할 경우 그 길이가 2²(=4), QPSK 변조 방식을 사용할 경우 그 길이가 2²(=16), 8PSK 변조 방식을 사용할 경우 그 길이라 2²(=16), 8PSK 변조 방식을 사용할 경우 그 길이가 2²(=16), 8PSK 변조 방식을

일반적으로, 무선 통신 시스템에서는 프리앰블을 사용하여 송수신기간의 동기 획득 및 채널 추정을 수행하며, 프레임의 시작 부분을 확인하게 된다. 현재 초광대역 무선 통신 시스템에는 프리앰블로 길이 16의 CAZAC 시퀀스를 사용하도록 제안되어 있다. 그러나, 변조 방식으로 QPSK 방식을 사용하게 되면, 상기 초광대역 통신 시스템의 송신기 및 수신기의 하드웨어 구현이 난이하고, 실제 송신기 및 수신기를 하드웨어적으로 구현할 경우 그 복잡도가 증가한다는 단점이 있다. 그래서, 상기 초광대역 통신 시스템에서는 변조방식으로 상기 QPSK 방식 대신 BPSK 방식을 사용하는 방안을 고려하고 있다. 이렇게 변조 방식으로 상기 BPSK 방식을 사용할경우 송신기 및 수신기의 하드웨어 구현은 용이하게 되나, 상기 CAZAC 시퀀스의 특성상 시퀀스 길이에 제한이 발생된다. 즉, 상기에서 설명한 바와 같이 변조 방식으로 BPSK 방식을 사용할경우 상기 CAZAC 시퀀스의 길이는 4로 제한된다. 상기 CAZAC 시퀀스는 시퀀스 특성상 상관도특성이 우수하고, 채널 추정에 우수하지만 변조 방식으로 BPSK 방식을 사용할경우 시퀀스 길이가 짧아 동기를 획득하는 것이 난이하다.

<50> 여기서, 길이가 4인 CAZAC 시퀀스를 프리앰블로 적용했을 경우 동기를 획득하는 것이 난이한 이유는 다음과 같다.

실이가 4인 CAZAC 시퀀스를 반복하여 길이 160의 프리앰블을 생성했을 경우, 상기 프리앰블을 이용하여 동기를 획득하는 과정에서 실제 동기가 일치한다고 하더라도 그 상관도 값이 실제 동기가 일치하지 않을 경우 획득되는 상관도 값에 비해서 상대적으로 큰 차이를 가지지 않는다. 그래서, 동기가 일치하는 시점을 정확하게 판단하는 것이 난이하고, 따라서 동기를 획득하는 것 역시 난이해지는 것이다. 그러므로, 상기 길이 4의 CAZAC 시퀀스를 프리앰블로 사용하지 않고도 동기를 획득하기 위한 새로운 프리앰블에 대한 필요성이 대두되고 있다.

## 【발명이 이루고자 하는 기술적 과제】

- <52> 따라서, 본 발명의 목적은 초광대역 통신 시스템에서 프리앰블을 생성하는 장치 및 방법을 제공함에 있다.

- 본 발명의 다른 목적은 초광대역 통신 시스템에서 동기 획득용 프리앰블과 채널 추정용 프리앰블을 분리하여 생성하는 장치 및 방법을 제공함에 있다.

- 본 발명의 또 다른 목적은 초광대역 통신 시스템에서 프리앰블을 그 목적에 따라 비주기적 시퀀스 혹은 주기적 시퀀스를 사용하여 생성하는 장치 및 방법을 제공함에 있다.

- 상기한 목적들을 달성하기 위한 본 발명의 제1실시예에 따른 송신 장치는; 초광대역 통신 시스템의 프리앰블 송신 장치에 있어서, 비주기적 상관 특성을 가지는 비주기적 시퀀스를 사용하여 동기 획득용 프리앰블인 제1프리앰블을 생성하는 제1프리앰블 발생기와, 상기 비주기적 시퀀스를 사용하여 채널 추정용 프리앰블인 제2프리앰블을 생성하는 제2프리앰블 발생기와.

상기 제1프리앰블과 상기 제2프리앰블을 다중화하여 상기 초광대역 통신 시스템의 프리앰블로 송신하는 송신기를 포함함을 특징으로 한다.

상기한 목적들을 달성하기 위한 본 발명의 제2실시예에 따른 송신 장치는; 초광대역 통신 시스템의 프리앰블 송신 장치에 있어서, 비주기적 상관 특성을 가지는 비주기적 시퀀스를 사용하여 동기 획득용 프리앰블인 제1프리앰블을 생성하는 제1프리앰블 발생기와, 주기적 상관 특성을 가지는 주기적 시퀀스를 사용하여 채널 추정용 프리앰블인 제2프리앰블을 생성하는 제2 프리앰블 발생기와, 상기 제1프리앰블과 상기 제2프리앰블을 다중화하여 상기 초광대역 통신시스템의 프리앰블로 송신하는 송신기를 포함함을 특징으로 한다.

상기한 목적들을 달성하기 위한 본 발명의 제1실시예에 따른 송신 방법은; 초광대역 통신 시스템의 프리앰블 송신 방법에 있어서, 비주기적 상관 특성을 가지는 비주기적 시퀀스를 사용하여 동기 획득용 프리앰블인 제1프리앰블을 생성하는 과정과, 상기 비주기적 시퀀스를 사용하여 채널 추정용 프리앰블인 제2프리앰블을 생성하는 과정과, 상기 제1프리앰블과 상기 제2 프리앰블을 다중화하여 상기 초광대역 통신 시스템의 프리앰블로 송신하는 과정을 포함함을 특징으로 한다.

\*\*\* 상기한 목적들을 달성하기 위한 본 발명의 제2실시예에 따른 송신 방법은; 초광대역 통신 시스템의 프리앰블 송신 방법에 있어서, 비주기적 상관 특성을 가지는 비주기적 시퀀스를 사용하여 동기 획득용 프리앰블인 제1프리앰블을 생성하는 과정과, 주기적 상관 특성을 가지는 주기적 시퀀스를 사용하여 채널 추정용 프리앰블인 제2프리앰블을 생성하는 과정과, 상기 제1 프리앰블과 상기 제2프리앰블을 다중화하여 상기 초광대역 통신 시스템의 프리앰블로 송신하는 과정을 포함함을 특징으로 한다.

\*59> 상기한 목적들을 달성하기 위한 본 발명의 수신 장치는; 초광대역 통신 시스템의 프리앰 블 수신 장치에 있어서, 수신 신호를 역다중화하여 동기 획득용 프리앰블인 제1프리앰블과 채 널 추정용 프리앰블인 제2프리앰블과, 데이터로 출력하는 역다중화기와, 상기 제1프리앰블을 가지고 동기 획득을 수행하고, 상기 동기 획득 수행 결과에 따른 동기 정보를 출력하는 상관도 검사기와, 상기 제2프리앰블을 가지고 채널 추정을 수행하고, 상기 채널 추정 결과에 따른 채 널 추정값을 출력하는 채널 추정기와, 상기 동기 정보와 상기 채널 추정값을 가지고 상기 데이터를 원래 정보 데이터로 복원하는 데이터 복원기를 포함함을 특징으로 한다.

\*60> 상기한 목적들을 달성하기 위한 본 발명의 수신 방법은; 초광대역 통신 시스템의 프리앰 블 수신 방법에 있어서, 수신 신호를 역다중화하여 동기 획득용 프리앰블인 제1프리앰블과 채 널 추정용 프리앰블인 제2프리앰블과, 데이터로 출력하는 과정과, 상기 제1프리앰블을 가지고 동기 획득을 수행하고, 상기 동기 획득 수행 결과에 따른 동기 정보를 출력하는 과정과, 상기 제2프리앰블을 가지고 채널 추정을 수행하고, 상기 채널 추정 결과에 따른 채널 추정값을 출력하는 과정과, 상기 동기 정보와 상기 채널 추정값을 가지고 상기 데이터를 원래 정보 데이터로 복원하는 과정을 포함함을 특징으로 한다.

#### 【발명의 구성 및 작용】

이하, 본 발명에 따른 바람직한 실시예를 첨부한 도면을 참조하여 상세히 설명한다. 하기의 설명에서는 본 발명에 따른 동작을 이해하는데 필요한 부분만이 설명되며 그 이외 부분의설명은 본 발명의 요지를 흩트리지 않도록 생략될 것이라는 것을 유의하여야 한다.

<62> 본 발명은 초광대역(UWB: Ultra Wide Band) 통신 시스템의 프리앰블(preamble)을 동기 획득용과, 채널 추정(channel estimation)용으로 분할하고, 상기 동기 획득용으로 사용되는 프 리앰블과 채널 추정용으로 사용되는 프리앰블 각각의 특성에 상응하도록 프리앰블을 생성하는 방법을 제안한다. 이하, 설명의 편의상 상기 동기 획득용으로 사용되는 프리앰블을 "제1프리앰 블"이라 칭하기로 하며, 상기 채널 추정용으로 사용되는 프리앰블을 "제2프리앰블"이라 칭하기 로 한다. 특히, 본 발명은 제1프리앰블을 비주기적(apreiodic) 시퀀스를 사용하여 생성하고, 제2프리앰블 역시 비주기적 시퀀스를 사용하여 생성하는 제1실시예와, 제1프리앰블을 비주기적 (apreiodic) 시퀀스를 사용하여 생성하고, 제2프리앰블은 주기적(preiodic) 시퀀스를 사용하여 생성하는 제2실시예의 두가지 실시예들을 가진다. 본 발명에서는 상기 비주기적 시퀀스로서 비 주기적 순환 다중화(ARM: Apreiodic Recursive Multiplex, 이하 "ARM"이라 칭하기로 한다) 시 퀀스를 사용하는 경우를 가정하며, 상기 주기적 시퀀스로서 CAZAC(Constant Amplitude Zero Auto Correlation) 시퀀스를 사용하는 경우를 가정하여 설명하기로 하며, 상기 비주기적 시퀀 스로서 상기 ARM 시퀀스 이외의 비주기적 특성을 가지는 어떤 시퀀스라도 사용 가능하며, 또한 상기 주기적 시퀀스로서 상기 CAZAC 시퀀스 이외의 주기적 특성을 가지는 어떤 시퀀스를 사용 가능함은 물론이다. 따라서, 본 발명의 제1실시예는 제1프리앰블 및 제2프리앰블 모두를 ARM 시퀀스를 사용하여 생성하고, 본 발명의 제2실시예는 제1프리앰블을 ARM 시퀀스를 사용하여 생 성하고, 제2프리앰블을 CAZAC 시퀀스를 사용하여 생성한다.

<63> 도 9는 본 발명의 실시예에 따른 초광대역 통신 시스템의 물리 계층 프레임 구조를 개략 적으로 도시한 도면이다.

'64' 상기 도 9를 설명하기에 앞서, 상기 물리 계층 프레임은 종래 기술 부분에서 설명한 바와 같이 상기 물리 계층 프레임은 프리앰블과, 물리(PHY: physical, 이하 "PHY"라 칭하기로 한

다) 해더(header)와, 매체 접속 제어(MAC: Media Access Control, 이하 "MAC"이라 칭하기로 한다)에더와, 해더 검사 시퀀스(HCS: Header Check Sequence, 이하 "HCS"라 칭하기로 한다)와, 데이터 + 프레임 검사 시퀀스(FSC: Frame Check Sequence, 이하 "FCS"라 칭하기로 한다)와, 스터브 비트들(SB: Stuff Bits, 이하 "SB"라 칭하기로 한다)과, 테일 심벌들(TS: Tail Symbols, 이하 "TS"라 칭하기로 한다)로 구성된다. 상기와 같은 물리 계층 프레임 구조는 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우 및 55Mb/s일 경우에 적용되는 것이며, 전송 속도가 11Mb/s일 경우에는 상기 전송 속도가 22Mb/s일 경우와, 33Mb/s일 경우와, 44Mb/s일 경우 및 55Mb/s일 경우와는 다르게 프리앰블과, PHY 헤더 + MAC 헤더 + HCS와, PHY 헤더 + MAC 헤더 + HCS와, 데이터 + FCS 및 TS로 구성된다. 이하, 본 발명을 설명함에 있어 상기 물리 계층 프레임 구조에서 상기 프리앰블을 제외한 나머지 신호들은 모두 "물리 데이터"라 칭하기로 한다.

상기 도 9를 참조하면, 먼저 상기 물리 계층 프레임은 프리앰블(preamble)(910)과, 물리데이터(920)로 구분된다. 또한, 상기 프리앰블(910)은 제1프리앰블(930)과, 제2프리앰블(940)로 구성된다. 상기 제1프리앰블(930)은 송신기와 수신기간의 동기 획득을 위해 사용되며, 상기제2프리앰블(940)은 채널 추정을 위해 사용된다. 여기서, 본 발명의 제1실시예에서는 상기 제1프리앰블(930)및 제2프리앰블(940)모두를 자기 상관(autocorrelation)특성이 우수한 비주기적 시퀀스를 사용하여 생성하며, 본 발명의 제2실시예에서는 상기 제1프리앰블(930)은 주기 상관 특성이 우수한 비주기적 시퀀스를 사용하여 생성하며, 제2프리앰블(940)은 채널 추정 특성이 우수한 주기적 시퀀스를 사용하여 생성한다. 상기 종래 기술 부분에서 설명한 바와 같이 현재 초광대역 통신 시스템은 프리앰블로서 CAZAC 시퀀스를 사용하고, 변조 방식으로 QPSK(Quadroture Phase Shift Keying) 방식을 사용하도록 제안되어 있다. 상기 초광대역 통신

시스템에서 변조방식으로 QPSK 방식을 사용할 경우 송신기 및 수신기의 하드웨어 구현이 난이하고, 실제 송신기 및 수신기를 하드웨어적으로 구현한다고 할 경우라도 복잡도가 증가하기 때문에 상기 QPSK 방식을 사용하는 것은 난이하여 BPSK 방식을 사용하는 것을 고려하고 있다. 그러나, 상기 BPSK 방식을 사용할 경우 상기 CAZAC 시퀀스 특성상 길이 4의 시퀀스로 시퀀스 길이가 한정되고, 상기 길이 4의 CAZAC 시퀀스를 프리앰블로 사용하는 것은 상기 종래 기술 부분에서 설명한 바와 같이 동기 획득을 난이하게 한다는 단점을 가진다. 따라서, 본 발명에서는 상기 프리앰블(910)을 동기 획득을 위한 제1프리앰블(930)과, 채널 추정을 위한 제2프리앰블 (940)로 분할하여, 상기 제1프리앰블(930)은 비주기적 시퀀스인 ARM 시퀀스를 사용하여 생성하고, 상기 제2프리앰블(940)은 ARM 시퀀스를 사용하여 생성하다.

- -66> 그러면 여기서 상기 주기적 시퀀스의 자기 상관 특성을 도 10을 참조하여 설명하기로 한다.

- <67> 상기 도 10은 주기적 시퀀스 자기 상관도 검출을 개략적으로 도시한 도면이다.

- 68> 상기 도 10을 설명하기에 앞서, 일반적으로 수신 신호의 동기가 획득??는지 여부는 수신 신호의 자기 상관 함수를 사용하여 판단할 수 있다. 비연속 전송을 위한 상관도에서는 두 가 지의 상관도 계산 방식이 있다. 첫 번째 방식은 주기적 상관도 계산이고, 두 번째 방식은 비주 기적 상관도 계산 방식이다. 이렇게 상기 두 가지 상관도 계산 방식증 어느 방식을 사용하여 자기 상관도를 계산할지는 자기 상관도를 구하고자 하는 신호의 특성에 따라서 결정된다. 상기 도 10은 상기 주기적 상관도 계산 방식에 상응하게 자기 상관도를 검출하는 방식을 도시하고 있는 것이다.

상기 도 10을 참조하면, 먼저 상관도 구간은 수신 신호에 대한 상관도를 측정하기 위한 전체 구간을 나타낸다. 상기 상관도 구간중 유효 상관도 구간은 수신 신호들간의 자기 상관도를 계산할 때 실질적으로 영향을 미치는 구간을 나타낸다. 상기 유효 상관도 구간에서 자기 상관도를 구하면 하기 수학식 1과 같다.

#

상기 수학식 1에서, x(t)는 수신 신호를 나타나며, Rxx(τ)는 상기 수신신호 x(t)의 자기 상관 함수를 나타낸다. 상기 수학식 1에서, 상기 자기 상관 함수 Rxx(τ)는 t 시점과 t+τ에서 의 값의 곱을 미리 설정된, 충분히 큰 시간 T에 걸쳐 평균한 값이다. 이렇게, 상기 주기적 시 퀸스를 사용하는 경우 자기 상관 특성이 높을수록 우수한 특성을 가지게 되는 것이다.

성기 도 10에서는 주기적 상관도 계산 방식에 상응하게 자기 상관도를 검출하는 방식을 설명하였으며, 다음으로 도 11을 참조하여 상기 비주기적 시퀀스의 자기 상관 특성을 설명하기 로 한다.

<73> 상기 도 11은 비주기적 시퀀스의 자기 상관도 검출을 개략적으로 도시한 도면이다.

상기 도 11을 참조하면, 먼저 상관도 구간은 수신 신호에 대한 상관도를 측정하기 위한 전체 구간을 나타낸다. 상기 상관도 구간중 유효 상관도 구간은 수신 신호들간의 자기 상관도 를 계산할 때 실질적으로 영향을 미치는 구간을 나타낸다. 여기서, 상기 유효 상관도 구간은 상기 도 10에서 설명한 주기적 상관도 계산 방식의 유효 상관도 구간과는 상이하며, 그 이유는 상기 비주기적 시퀀스가 연속되어 수신되지 않기 때문이다. 즉, 상기 비주기적 상관도 계산 방 식에서는 수신 신호가 단일파라고 고려하고, 일정 시간 지연이 발생했을 때 상기 지연된 일정 시간만큼의 구간이 상기 유효 상관도 구간에서 제외되기 때문에 유효 상관도 구간이 줄어든다.

이는 상기 수신 신호가 지연된 후의 값들은 모두 "0"으로 설정된다는 것을 의미하는 것이다. 상기 유효 상관도 구간에서 상기 비주기적 상관도 계산 방식으로 자기 상관도를 구하면 하기 수학식 2와 같다.

상기에서 설명한 바와 같이 주기적 상관도 계산 방식과 비주기적 상관도 계산 방식간의 가장 큰 차이점은 자기 상관도를 계산함에 있어 유효 상관도 구간이 상이하다는 것이다. 즉, 상기 주기적 시퀀스를 사용할 경우 동일한 신호가 반복되어 수신된다고 가정하기 때문에 유효 상관도 구간이 지속되기 때문에 상기 반복된 동일한 신호들이 자기 상관도를 구하는데 영향을 미치지만, 상기 비주기적 시퀀스를 사용할 경우 특정 신호가 한번만 수신된다고 가정하기 때문에 상기 신호 이후에 연속적으로 수신되는 다른 신호들은 자기 상관도를 구하는데 영향을 미치지 않는다. 일 예로, 길이 4인 CAZAC 시퀀스 1101을 가지고 주기적 자기 상관도와 비주기적 자기 상관도를 구하면 하기와 같다. 여기서, 수신 신호의 지연 시간은 1심벌 길이라고 가정하기로 한다.

<78>

한편, 상기 초광대역 통신 시스템의 표준 규격인 IEEE 802.15.3a에서는 길이 16의 CAZAC 시퀀스를 프리앰블로 사용하도록 하고 있으나, 상기에서 설명한 바와 같이 다수의 문제점들로 인해서 본 발명에서는 상기 프리앰블에 128비트의 비주기적 ARM 시퀀스를 사용하는 것을 제안한다. 이를 상세하게 설명하면, 길이 4의 CAZAC 시퀀스를 동기 획득에 사용하기 위해서는 상기길이 4의 CAZAC 시퀀스를 반복함으로써 길이를 늘릴수 있으나, 상기 CAZAC 시퀀스의 특성상주기적 자기 상관도를 구하면 동기를 획득하였다 할지라도 동기를 획득하지 못했을 경우와 비교하여 주기적 자기 상관도가 높지 않아 실제 동기가 획득되었는지 여부를 판단하는 것이 난이하다. 즉, 상기 길이 4의 CAZAC 시퀀스를 반복하여 전송할 경우 주기적 자기 상관도를 구하면

동기를 획득했을 때 출력되는 자기 상관도에 비해 상기 길이 4의 CAZAC 시퀀스만큼 지연되어 있는 시점에서 구한 자기 상관도가 상기 CAZAC 시퀀스의 길이만큼 차이를 나타낸다. 결국, 상기 초광대역 통신 시스템에서 BPSK 방식을 사용할 경우 상기 길이 4의 CAZAC 시퀀스를 반복하여 프리앰블을 전송할 경우 동기를 획득했을때와 동기를 획득하지 못했을 때의 자기 상관도들 간에는 4의 차이를 가지게 되며, 4라는 차이는 에너지 레벨(energy level)에서 실제 구별하는 것이 난이하고, 따라서 동기 획득을 정확하게 검출할 수 없을 수도 있다는 단점을 가지게 된다

- 스러면 여기서 상기 제1프리앰블(930)에 사용할 비주기적 시퀀스, 즉 ARM 시퀀스를 생성하는 장치를 도 12를 참조하여 설명하기로 한다.

- <82> 도 12는 도 9의 제1프리앰블(930)에 적용할 ARM 시퀀스 생성 장치 내부 구조를 도시한 도면이다.

- 상기 도 12는 특히 길이 128의 ARM 시퀀스를 생성하는 장치로서, 먼저, 2비트의 모든 가능한 실수의 조합(00 또는 01 또는 10 또는 11)중 하나가 입력 신호로 입력되면 그대로 상기입력 신호가 제1다중화기(1200)로 입력되고, 이와 동시에 상기 입력 신호가 배타적 논리합(XOR)가산기(1205)로 입력된다. 또한, 이와 동시에 신호 발생기(1203)는 01 또는 10의 신호를 발생하여 상기 배타적 논리합 가산기(1205)로 출력한다. 상기 배타적 논리합 가산기(1205)는 상기 신호 발생기(1203)에서 출력한 신호와 상기 입력 신호를 배타적 논리합하여 상기 제1다중화기(1200)로 출력한다. 상기 제1다중화기(1200)는 상기 입력 신호와 상기 배타적 논리합 가산기(1205)에서 출력한 신호를 시간적으로 번갈아 다중화하여 4비트의 ARM 시퀀스를 생성하고, 상기 생성한 4비트 ARM 시퀀스를 제2다중화기(1210)와 배타적 논리합 가산기(1215)로 출력한다

이렇게, 상기 제1다중화기(1200)에서 제2다중화기(1210)로 4비트 ARM 시퀀스가 입력됨과 동시에, 신호 발생기(1213)는 0101 또는 1010의 신호를 발생하여 상기 배타적 논리합 가산기 (1215)로 출력한다. 상기 배타적 논리합 가산기(1215)는 상기 신호 발생기(1213)에서 출력한 신호와 상기 제1다중화기(1200)에서 출력한 4비트 ARM 시퀀스를 배타적 논리합하여 상기 제2다중화기(1210)로 출력한다. 상기 제2다중화기(1210)는 상기 입력 신호와 상기 배타적 논리합 가산기(1215)에서 출력한 신호를 시간적으로 번갈아 다중화하여 8비트의 ARM 시퀀스를 생성하고, 상기 생성한 8비트 ARM 시퀀스를 제3다중화기(1220)와 배타적 논리합 가산기(1225)로 출력한다.

이렇게, 상기 제2다중화기(1210)에서 제3다중화기(1220)로 8비트 ARM 시퀀스가 입력됨과 동시에, 신호 발생기(1223)는 01010101 또는 10101010의 신호를 발생하여 상기 배타적 논리합 가산기(1225)로 출력한다. 상기 배타적 논리합 가산기(1225)는 상기 신호 발생기(1223)에서 출력한 신호와 상기 제2다중화기(1210)에서 출력한 8비트 ARM 시퀀스를 배타적 논리합하여 상기 제3다중화기(1220)로 출력한다. 상기 제3다중화기(1220)는 상기 입력 신호와 상기 배타적 논리합 가산기(1225)에서 출력한 신호를 시간적으로 번갈아 다중화하여 16비트의 ARM 시퀀스를 생성하고, 상기 생성한 16비트 ARM 시퀀스를 제4다중화기(1230)와 배타적 논리합 가산기(1235)로 출력한다.

이렇게, 상기 제3다중화기(1220)에서 제4다중화기(1230)로 16비트 ARM 시퀀스가 입력됨과 동시에, 신호 발생기(1233)는 010101010101010101 또는 101010101010101010의 신호를 발생하여 상기 배타적 논리합 가산기(1235)로 출력한다. 상기 배타적 논리합 가산기(1235)는 상기 신호 발생기(1233)에서 출력한 신호와 상기 제3다중화기(1220)에서 출력한 16비트 ARM 시퀀스를 배타적 논리합하여 상기 제4다중화기(1230)로 출력한다. 상기 제4다중화기(1230)는 상기 입력 신

호와 상기 배타적 논리합 가산기(1235)에서 출력한 신호를 시간적으로 번갈아 다중화하여 32비트의 ARM 시퀀스를 생성하고, 상기 생성한 32비트 ARM 시퀀스를 제5다중화기(1240)와 배타적 논리합 가산기(1245)로 출력한다.

<87> 이렇게, 상기 제4다중화기(1230)에서 제5다중화기(1240)로 32비트 ARM 시퀀스가 입력됨

과 동시에, 신호 발생기(1243)는 010101010101010101010101010101

또는

·88> 이렇게, 상기 제5다중화기(1240)에서 제6다중화기(1250)로 64비트 ARM 시퀀스가 입력됨 과 동시에, 신호 발생기(1253)는

설명하였으나, 256, 512, ... 등과 같은 2의 멱승을 가지는 길이의 ARM 시퀀스는 상기 도 12에서 설명한 바와 같은 구조를 확장할 경우 생성 가능함은 물론이다.

어마다 사람이로 도 13을 참조하여 본 발명의 실시예에 따른 물리 계층 프레임 생성 장치를 설명하기로 한다.

<90> 상기 도 13은 도 9의 물리 계층 프레임을 송신하는 물리 계층 프레임 송신 장치 내부 구조를 개략적으로 도시한 도면이다.

《91》 상기 도 13을 설명하기에 앞서, 상기 도 13에 도시한 물리 계층 프레임 송신 장치는 상기 프리앰블만을 구체적으로 설명하기 위해서 상기 물리 계층 프레임에서 상기 프리앰블을 제외한 나머지 신호들, 즉 PHY 헤더와, MAC 헤더와, HCS와, 데이터 + FCS와, SB 및 TS를 "물리데이터"라고 정의하기로 한다.

역2> 먼저, 제1프리앰블 발생기(1300)는 상기 도 12에서 설명한 바와 같은 길이 128의 ARM 시 권스를 발생하여 다중화기(1330)로 출력한다. 또한, 제2프리앰블 발생기(1310)는 길이 32의 ARM 시퀀스를 발생하거나 혹은 길이 4의 CAZAC 시퀀스를 8번 반복하여 상기 다중화기(1330)로 출력한다. 여기서, 상기 본 발명의 제1실시예에서는 상기 제2프리앰블에는 ARM 시퀀스를 사용하므로 상기 본 발명의 제1실시예가 적용될 경우 상기 제2프리앰블 발생기(1310)는 길이 32의 ARM 시퀀스를 발생하고, 이와는 달리 상기 본 발명의 제2실시예에서는 상기 제2프리앰블에는 CAZAC 시퀀스를 사용하므로 본 발명의 제2실시예가 적용될 경우 상기 제2프리앰블 발생기 (1310)는 길이 4의 CAZAC 시퀀스를 8번 반복 발생한다. 그리고, 상기 제1프리앰블 길이가 128이기 때문에, 상기 제2프리앰블 길이는 자동적으로 32가 되며, 따라서 길이 4의 CAZAC 시퀀스는 8번 반복되어 상기 제2프리앰블로 생성되는 것이다. 상기 다중화기(1330)는 상기 제1프리앰블 발생기(1300)에서 출력한 제1프리앰블과, 상기

제2프리앰블 발생기(1310)에서 출력한 제2프리앰블을 상기 도 9에서 설명한 바와 같은 물리 계층 프레임 구조에 상응하게 다중화한 후 다중화기(1340)로 출력한다. 한편, 물리 데이터(1320)역시 상기 다중화기(1340)로 입력되고, 상기 다중화기(1340)는 상기 다중화기(1330)에서 출력한 신호, 즉 프리앰블과 상기 물리 데이터(1320)를 상기 도 9에서 설명한 바와 같은 물리 계층 프레임 구조에 상응하게 다중화하여 물리 계층 프레임으로 생성하여 출력한다.

<93> 상기 도 13에서는 물리 계층 프레임 송신 장치 내부 구조를 설명하였으며, 다음으로 도 14를 참조하여 상기 물리 계층 프레임을 생성하는 과정을 설명하기로 한다.

<94> 상기 도 14는 도 13에 상응하는 물리 계층 프레임 송신 과정을 도시한 순서도이다.

상기 도 14를 참조하면, 먼저 상기 도 13에서 설명한 바와 같은 물리 계층 프레임 송신 장치는 1400단계에서 동기 획득용인 제1프리앰블을 생성하고 1420단계로 진행한다. 또한, 상기물리 계층 프레임 송신 장치는 1410단계에서 채널 추정용인 제2프리앰블을 생성하고 1420단계로 진행한다. 상기 1420단계에서 상기 물리 계층 프레임 송신 장치는 상기 생성된 제1프리앰블과 제2프리앰블을 시간적으로 연집하여 프리앰블로서 생성하고 1430단계로 진행한다. 상기 1430단계에서 상기물리 계층 프레임 송신 장치는 상기 생성된 프리앰블과 물리 데이터를 상기도 9에서 설명한 물리 계층 프레임 구조에 상응하게 다중화하여 물리 계층 프레임으로 생성하고 1440단계로 진행한다. 상기 1440단계에서 상기물리 계층 프레임 송신 장치는 상기 생성된 물리 계층 프레임을 에어(air)상으로 전송하고 종료한다.

상기 도 13 및 도 14에서는 물리 계층 프레임 송신 장치 및 송신 방법에 대해서 설명하였으며, 다음으로 도 15 및 도 16을 참조하여 물리 계층 프레임 수신 장치 및 수신 방법에 대해서 설명하기로 한다.

<97> 상기 도 15는 도 13에 상응하는 물리 계층 프레임 수신 장치 내부 구조를 개략적으로 도시한 도면이다.

〈98〉 상기 도 15를 참조하면, 먼저 에어상으로부터 물리 계층 프레임(1500)이 수신되면, 상기 수신된 물리 계층 프레임(1500)은 역다중화기(DEMUX)(1510)로 입력된다. 상기 역다중화기 (1510)는 상기 물리 계층 프레임(1500)을 상기 도 9에서 설명한 물리 계층 프레임 구조에 상응하게 역다중하여 프리앰블은 역다중화기(1520)로 출력하고, 물리 데이터는 데이터 복원기 (1550)로 출력한다. 상기 역다중화기(1520)는 상기 역다중화기(1510)에서 출력한 프리앰블을 상기 도 9에서 설명한 물리 계층 프레임 구조에 상응하게 역다중하여 제1프리앰블은 상관도 검사기(1530)로 출력하고, 제2프리앰블은 채널 추정기(channel estimator)(1540)로 출력한다.

생기 상관도 검사기(1530)는 상기 역다중화기(1520)에서 출력한 제1프리앰블을 가지고 자기 상관도를 검사하고, 상기 자기 상관도 검사 결과 미리 설정한 설정 상관도를 초과할 경우 동기가 획득되었다고 판단하며, 상기 획득된 동기 정보(1570)를 상기 채널 추정기(1540) 및 데 이터 복원기(1550)로 출력한다. 한편, 상기 채널 추정기(1540)는 상기 역다중화기(1520)에서 출력한 제2프리앰블과, 상기 상관도 검사기(1530)에서 출력한 동기 정보(1570)를 가지고 채널 추정하고, 그 채널 추정 결과를 상기 데이터 복원기(1550)로 출력한다. 상기 데이터 복원기 (1550)는 상기 상관도 검사기(1530)에서 출력한 동기 정보(1570)와, 상기 채널 추정기(1540)에서 출력한 채널 추정 정보를 가지고 상기 역다중화기(1510)에서 출력한 물리 데이터를 복원하 여 실제 복원된 물리 데이터(1560)로 출력한다. 물론, 상기 상관도 검사기(1530)에서 검사 결과 동기가 획득되지 않았을 경우에는 더 이상의 동작, 즉 채널 추정 및 물리 데이터 복원 등의 동작을 수행하지 않는다.

<100> 상기 도 15에서는 물리 계층 프레임 수신 장치에 대해서 설명하였으며, 다음으로 도 16 을 참조하여 물리 계층 프레임 수신 과정에 대해서 설명하기로 한다.

<101> 상기 도 16은 도 15에 상응하는 물리 계층 프레임 수신 과정을 도시한 순서도이다.

상기 도 16을 참조하면, 먼저 1600단계에서 에어상으로부터 물리 계층 프레임을 수신하면 물리 계층 프레임 수신 장치는 1610단계로 진행한다. 상기 1610단계에서 상기 물리 계층 프레임 수신 장치는 상기 수신한 물리 계층 프레임을 상기 도 9에서 설명한 물리 계층 프레임 구조에 상응하게 역다중화하여 제1프리앰블과, 제2프리앰블 및 물리 데이터로 역다중화한다. 이렇게 역다중화된 제1프리앰블을 이용하여 상기 물리 계층 프레임 수신 장치는 동기 획득 과정을 수행하여 동기 정보를 검출한후 1640단계로 진행한다. 또한, 상기 역다중화된 제2프리앰블을 이용하여 상기 물리 계층 프레임 수신 장치는 점 결찰한 후 상기 1640단계로 진행한다. 생기 물리 계층 프레임 수신 장치는 상기 동기 정보와 채널 추정값을 검출한 후 상기 1640단계로 진행한다. 상기 물리 데이터로 복원하고 종료한다.

한편 본 발명의 상세한 설명에서는 구체적인 실시예에 관해 설명하였으나, 본 발명의 범위에서 벗어나지 않는 한도내에서 여러 가지 변형이 가능함은 물론이다. 그러므로 본 발명의 범위는 설명된 실시예에 국한되어 정해져서는 안되며 후술하는 특허청구의 범위뿐만 아니라 이 특허청구의 범위와 균등한 것들에 의해 정해져야 한다.

## 【발명의 효과】

\*\* 상술한 바와 같은 본 발명은, 초광대역 통신 시스템에서 물리 계층 프레임의 프리앰블을 동기 획득용 프리앰블과 채널 추정용 프리앰블로 분할하여 각각의 특성에 맞도록 비주기적 시퀀스 혹은 주기적 시퀀스를 적용함으로써 동기 획득 및 채널 추정 효율을 증가시킨다는 이점을 가진다. 특히, 초광대역 통신 시스템이 변조 방식으로 BPSK 방식을 사용할 경우 현재 사용되고 있는 CAZAC 시퀀스의 경우 동기 획득에 적합하지 않았으나, 본 발명과 같이 동기 획득용으로 사용되는 프리앰블에는 ARM 시퀀스를 사용하고 채널 추정용으로 사용되는 프리앰블에는 ARM 시퀀스 혹은 CAZAC 시퀀스를 무선 채널 상황에 적합하게 사용함으로써 동기 획득 및 채널 추정효율을 증가시키고, 이에 따라 상기 초광대역 통신 시스템 전체 시스템 성능을 향상시킨다는 이점을 가진다.

#### 【특허청구범위】

## 【청구항 1】

초광대역 통신 시스템의 프리앰블 송신 장치에 있어서,

비주기적 상관 특성을 가지는 비주기적 시퀀스를 사용하여 동기 획득용 프리앰블인 제1 프리앰블을 생성하는 제1프리앰블 발생기와,

상기 비주기적 시퀀스를 사용하여 채널 추정용 프리앰블인 제2프리앰블을 생성하는 제2 프리앰블 발생기와,

상기 제1프리앰블과 상기 제2프리앰블을 다중화하여 상기 초광대역 통신 시스템의 프리앰블로 송신하는 송신기를 포함함을 특징으로 하는 초광대역 통신 시스템의 프리앰블 송신 장치.

#### 【청구항 2】

제1항에 있어서.

상기 비주기적 시퀀스는 비주기적 순환 다중화(ARM: Apreiodic Recursive Multiplex) 시 퀀스임을 특징으로 하는 초광대역 통신 시스템의 프리앰블 송신 장치.

## 【청구항 3】

초광대역 통신 시스템의 프리앰블 송신 장치에 있어서,

비주기적 상관 특성을 가지는 비주기적 시퀀스를 사용하여 동기 획득용 프리앰블인 제1 프리앰블을 생성하는 제1프리앰블 발생기와,

주기적 상관 특성을 가지는 주기적 시퀀스를 사용하여 채널 추정용 프리앰블인 제2프리앰블을 생성하는 제2프리앰블 발생기와,

상기 제1프리앰블과 상기 제2프리앰블을 다중화하여 상기 초광대역 통신 시스템의 프리앰블로 송신하는 송신기를 포함함을 특징으로 하는 초광대역 통신 시스템의 프리앰블 송신 장치.

# 【청구항 4】

제3항에 있어서,

상기 비주기적 시퀀스는 비주기적 순환 다중화(ARM: Apreiodic Recursive Multiplex) 시 퀀스임을 특징으로 하는 초광대역 통신 시스템의 프리앰블 송신 장치.

#### 【청구항 5】

제3항에 있어서,

상기 주기적 시퀀스는 CAZAC(Constant Amplitude Zero Auto Correlation) 시퀀스임을 특징으로 하는 초광대역 통신 시스템의 프리앰블 송신 장치.

## 【청구항 6】

초광대역 통신 시스템의 프리앰블 수신 장치에 있어서,

수신 신호를 역다중화하여 동기 획득용 프리앰블인 제1프리앰블과 채널 추정용 프리앰블 인 제2프리앰블과, 데이터로 출력하는 역다중화기와.

상기 제1프리앰블을 가지고 동기 획득을 수행하고, 상기 동기 획득 수행 결과에 따른 동기 정보를 출력하는 상관도 검사기와,

상기 제2프리앰블을 가지고 채널 추정을 수행하고, 상기 채널 추정 결과에 따른 채널 추정값을 출력하는 채널 추정기와,

상기 동기 정보와 상기 채널 추정값을 가지고 상기 데이터를 원래 정보 데이터로 복원하는 데이터 복원기를 포함함을 특징으로 하는 초광대역 통신 시스템의 프리앰블 수신 장치.

## 【청구항 7】

제6항에 있어서,

상기 제1프리앰블 및 제2프리앰블은 비주기적 시퀀스이며, 상기 비주기적 시퀀스는 비주기적 순환 다중화(ARM: Apreiodic Recursive Multiplex) 시퀀스임을 특징으로 하는 초광대역 통신 시스템의 프리앰블 수신 장치.

#### 【청구항 8】

제6항에 있어서,

상기 제1프리앰블은 비주기적 시퀀스이며, 상기 비주기적 시퀀스는 비주기적 순환 다중화(ARM: Apreiodic Recursive Multiplex) 시퀀스임을 특징으로 하는 초광대역 통신 시스템의 프리앰블 수신 장치.

출력 일자: 2004/2/24

## 【청구항 9】

제6항에 있어서,

상기 제2프리앰블은 주기적 시퀀스이며, 상기 주기적 시퀀스는 CAZAC(Constant Amplitude Zero Auto Correlation) 시퀀스임을 특징으로 하는 초광대역 통신 시스템의 프리앰블 수신 장치.

## 【청구항 10】

초광대역 통신 시스템의 프리앰블 송신 방법에 있어서,

비주기적 상관 특성을 가지는 비주기적 시퀀스를 사용하여 동기 획득용 프리앰블인 제1 프리앰블을 생성하는 과정과.

상기 비주기적 시퀀스를 사용하여 채널 추정용 프리앰블인 제2프리앰블을 생성하는 과정과,

상기 제1프리앰블과 상기 제2프리앰블을 다중화하여 상기 초광대역 통신 시스템의 프리앰블로 송신하는 과정을 포함함을 특징으로 하는 초광대역 통신 시스템의 프리앰블 송신 방법.

## 【청구항 11】

제10항에 있어서,

상기 비주기적 시퀀스는 비주기적 순환 다중화(ARM: Apreiodic Recursive Multiplex) 시 퀀스임을 특징으로 하는 초광대역 통신 시스템의 프리앰블 송신 방법.

## 【청구항 12】

초광대역 통신 시스템의 프리앰블 송신 방법에 있어서,

비주기적 상관 특성을 가지는 비주기적 시퀀스를 사용하여 동기 획득용 프리앰블인 제1 프리앰블을 생성하는 과정과.

주기적 상관 특성을 가지는 주기적 시퀀스를 사용하여 채널 추정용 프리앰블인 제2프리앰블을 생성하는 과정과,

상기 제1프리앰블과 상기 제2프리앰블을 다중화하여 상기 초광대역 통신 시스템의 프리앰블로 송신하는 과정을 포함함을 특징으로 하는 초광대역 통신 시스템의 프리앰블 송신 방법.

## 【청구항 13】

제12항에 있어서.

상기 비주기적 시퀀스는 비주기적 순환 다중화(ARM: Apreiodic Recursive Multiplex) 시 퀀스임을 특징으로 하는 초광대역 통신 시스템의 프리앰블 송신 방법.

## 【청구항 14】

제12항에 있어서,

상기 주기적 시퀀스는 CAZAC(Constant Amplitude Zero Auto Correlation) 시퀀스임을 특징으로 하는 초광대역 통신 시스템의 프리앰블 송신 방법.

# 【청구항 15】

초광대역 통신 시스템의 프리앰블 수신 방법에 있어서,

수신 신호를 역다중화하여 동기 획득용 프리앰블인 제1프리앰블과 채널 추정용 프리앰블인 제2프리앰블과, 데이터로 출력하는 과정과,

상기 제1프리앰블을 가지고 동기 획득을 수행하고, 상기 동기 획득 수행 결과에 따른 동 기 정보를 출력하는 과정과,

상기 제2프리앰블을 가지고 채널 추정을 수행하고, 상기 채널 추정 결과에 따른 채널 추정값을 출력하는 과정과,

상기 동기 정보와 상기 채널 추정값을 가지고 상기 데이터를 원래 정보 데이터로 복원하는 과정을 포함함을 특징으로 하는 초광대역 통신 시스템의 프리앰블 수신 방법.

#### 【청구항 16】

제15항에 있어서.

상기 제1프리앰블 및 제2프리앰블은 비주기적 시퀀스이며, 상기 비주기적 시퀀스는 비주기적 순환 다중화(ARM: Apreiodic Recursive Multiplex) 시퀀스임을 특징으로 하는 초광대역 통신 시스템의 프리앰블 수신 방법.

# 【청구항 17】

제15항에 있어서,

상기 제1프리앰블은 비주기적 시퀀스이며, 상기 비주기적 시퀀스는 비주기적 순환 다중화(ARM: Apreiodic Recursive Multiplex) 시퀀스임을 특징으로 하는 초광대역 통신 시스템의 프리앰블 수신 방법.

# 【청구항 18】

제15항에 있어서,

상기 제2프리앰블은 주기적 시퀀스이며, 상기 주기적 시퀀스는 CAZAC(Constant Amplitude Zero Auto Correlation) 시퀀스임을 특징으로 하는 초광대역 통신 시스템의 프리앰블 수신 방법.

# 【도면】

[도 1]

[도 2]

|   | ∫200 | 210 ح           | 220 ح  | 230 ح | 240 ح   | 25( | 260 ح |

|---|------|-----------------|--------|-------|---------|-----|-------|

|   | 프리앰블 | PHY 헤더          | MAC 헤더 | нсѕ   | 데이터+FCS | SB  | TS    |

| , | 지핸수  | <del>&gt;</del> |        | L     |         |     | J     |

[도 3]

|      | 300 ح | <sub>/</sub> 310      | 320 ح                 | 330 ح   | 340 ح |  |  |  |

|------|-------|-----------------------|-----------------------|---------|-------|--|--|--|

| п    | E리앰블  | PHY 헤더+MAC 헤더<br>+HCS | PHY 헤더+MAC 헤더<br>+HCS | 데이터+FCS | TS    |  |  |  |

| 진행순서 |       |                       |                       |         |       |  |  |  |

# 【도 4】

# [도 5]

[도 6]

【도 7】

[도 8]

| CAZAC 시퀀스 요소 | VALUE  |

|--------------|--------|

| C0           | 1 + j  |

| C1           | 1 + j  |

| C2           | 1 + j  |

| C3           | 1 + j  |

| C4           | -1 + j |

| C5           | -1 - j |

| C6           | 1- j   |

| C7           | 1 + j  |

| C8           | -1 - j |

| C9           | 1 + j  |

| C10          | -1 - j |

| C11          | 1 + j  |

| C12          | 1 – j  |

| C13          | -1 - j |

| C14          | −1 + j |

| C15          | 1 + j  |

[도 9]

# 【도 10】

【도 11】

# [도 12]

## 【도 13】

# 【도 14】

# 【도 15】

# 【도 16】